what is pll in microcontroller|What is a Phase : Tagatay Phase-locked loop (PLL) circuits exist in a wide variety of high frequency applications, from simple clock clean-up circuits, to local oscillators (LOs) for high performance radio communication links, and ultrafast switching frequency synthesizers in vector network analyzers (VNA). -=Roulette=-===== This song's tuning is drop D; then all strings down one whole step (C-G-C-F-A-D); only played with steel string acoustic guitar Author/Artist: System Of A Down Album: Steal this Album Transcribed by: Benjamin Marschner Email:

[email protected] HP: www.systemofadowntabs.de.vu (if you want the other tabs from ALL Albums)

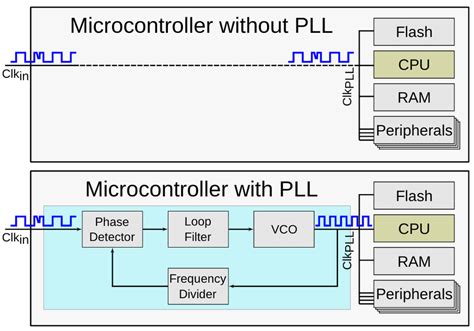

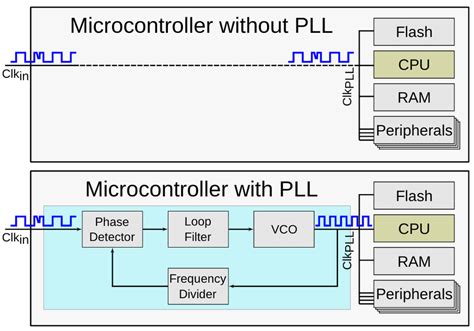

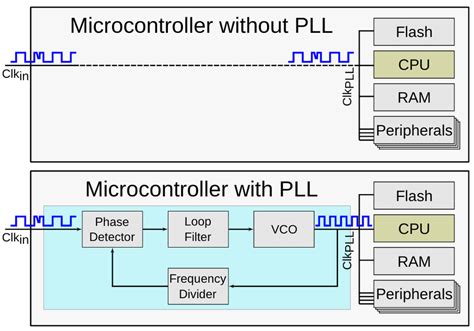

what is pll in microcontroller,Phase-locked loop (PLL) circuits exist in a wide variety of high frequency applications, from simple clock clean-up circuits, to local oscillators (LOs) for high performance radio communication links, and ultrafast switching frequency synthesizers in vector network analyzers (VNA).A phase-locked loop or phase lock loop (PLL) is a control system that generates an output signal whose phase is fixed relative to the phase of an input signal. Keeping the input and output phase in lockstep also implies keeping the input and output frequencies the same, thus a phase-locked loop can also track an input frequency. And by incorporating a frequency divider, a PLL can generate a stable frequency that is a multiple of the input frequency.

May 22, 2022 — A phase-locked loop (PLL) is a feedback system in which the frequency and phase of an output signal is related to the frequency and phase of an input signal. The block diagram of a PLL is shown in Figure \(\PageIndex{1}\).Mar 9, 2018 — The term “phase-locked loop” appears in a variety of contexts: microcontrollers, RF demodulators, oscillator modules, serial communications. The first thing to understand is that “PLL” does not refer to a single component.A phase-locked loop is a feedback system combining a voltage controlled oscillator (VCO) and a phase comparator so connected that the oscillator maintains a constant phase angle relative .

At its simplest, a phase-locked loop is a closed-loop feedback control circuit that's both frequency- and phase-sensitive. A PLL is not a single component, but a system that consists .

This video series will explain the building blocks for phase lock loops (PLL's) such as VCO’s, integer and fractional N frequency dividers, phase detectors and charge pumps.The phase locked loop or PLL is an electronic circuit with a voltage controlled oscillator, whose output frequency is continuously adjusted according to the input signal’s frequency. A Phase locked loop is used for tracking phase and .

What is a PhaseHun 13, 2024 — A phase-locked loop (PLL) is a feedback circuit designed to allow one circuit board to synchronize the phase of its on board clock with an external timing signal. PLL .A Phase-Locked Loop (PLL) is a device consisting of a phase detector, VCO, and low-pass filter, forming a servo loop where the VCO synchronizes with the input signal's frequency. It corrects .The phase-locked loop (PLL) is an interesting device. As shown in Figure 3-11, it consists of a phase detector, VCO, and low-pass filter.This comprises a servo loop, where the VCO is phase-locked to the input signal and oscillates at the same frequency. If there is a phase or frequency difference between the two sources, the phase detector produces an output that is used to .Hun 26, 2019 — This video explains Clocking MCU by Internal PLL(Running MCU at Full Speed). STM32F4xx based MCU is used in this video and it clearly explains all the PLL aspects of the Microcontroller. PLL is a clock generation .

A PLL may also have a frequency divider in its feedback loop in order to create an output that is a multiple of the reference frequency instead of one that is exactly equal to it. Block diagram of a basic phase-locked loop, with phase detector, loop filter, VCO, and optional frequency divider. What are the three stages through which a PLL operates?

May 2, 2023 — I am trying to implement a Phase Locked Loop in a microcontroller STM32. I have a reference signal and feedback signal which has $\phi$ difference wrt reference signal. For the moment, I am not using a real time feedback signal, rather simulating it inside the microcontroller itself, but later extend this to Real time. 1.Ene 23, 2020 — In this video, the basics of the Phase Lock Loop (PLL) have been explained.By watching this video, you will learn the following topics:0:00 Introduction0:20 .Okt 12, 2017 — In a ST microcontroller I'm using there are two OSC's that can be routed to exactly the same hardware and I'm wondering when you would use each one. Link to part documentation STM32L496ZG. Excerpt from the data sheet about the two OSC's --16 MHz high-speed internal RC oscillator (HSI16), trimmable by software, that can supply a PLLDis 8, 2020 — Plls in network analyzers. The ability of the PLL to reliably generate high-frequency signals makes it a great candidate for network analyzer signal sources. You can easily sweep across broad frequency ranges by adjusting N. The figure below shows a general network analyzer block diagram with a PLL-based source.

Hun 24, 2014 — The quoted sentence sounds it's referring to the "limp mode" which is implemented in some microcontroller's PLL circuitry. If the reference clock fails by either stopping altogether or running at a speed which is nowhere near correct, the PLL will switch to a "limp mode" in which it ignores the reference clock and instead operates at a speed which is .When we use PLL, we can increase the clock speed of the TM4C123 manyfold. The TM4C123 has a 400MHz PLL. Means it can generate a maximum of 400MHz depending on what is the applied input clock to the PLL. As told before the PLL can accept clock from only 2 of the above-mentioned sources. External Crystal; Precision Internal Oscillatorwhat is pll in microcontrollerPeb 6, 2022 — PLL`s are necessary for receiving and processing signals having very small amplitudes - for example, for communcation with satellites and deep space probes. Because of such small amplitudes - and the unavoidable noise disturbances - it is absolutely necessary to keep the receiving bandwidth as small as possible.

what is pll in microcontroller What is a PhasePLL allows changing frequency dynamically. In LPC2148 microcontrollers there are two PLLs which provide programmable frequencies to the CPU and USB System. [PLL0: For System Clock, PLL1: For USB Clock] Basic PLL in .

Hul 13, 2016 — The crystal oscillator feeds into an on-chip Phased Locked Loop (PLL) which can multiply and divide the crystal frequency by values between 1 and 16. So with a 8MHz crystal you can generate a 48MHz main clock for the .– 48MHz from PLL for Full-speed Bus Operation – USB Bus Connection/Disconnection on Microcontroller Request – Crystal-less operation for Low Speed mode • Peripheral Features – On-chip PLL for USB and High Speed Timer: 32 up to 96MHz operation – One 8-bit Timer/Counter with Separate Prescaler and Compare Mode ATmega16U4/ATmega32U4

Abr 21, 2008 — The Phase Locked Loop or PLL is a feedback system used in high quality stereo decoders, Frequency shift keying, telemetry applications, wide band FM discriminators, frequency multiplication applications etc. PLL integrated circuits are now available to minimize the component count. This note will give the working principle of PLL integrated circuits. 1. .with 3 independent outputs. The input clock of the PLL can be selected between HSI and HSE. The main PLL can provide the system clock. The different PLL outputs can be used for the serial audio interfaces, USB, Random Number Generator, SDMMC peripherals and LTDC/ and DSI-HOST interfaces when available. 10lines with up to nine external interrupt pins these microcontrollers are particularly suitable for automotive and industrial control applications, as well as medical systems and fault-tolerant maintenance buses. With a wide range of additional serial communications

A prescaler is an electronic counting circuit used to reduce a high frequency electrical signal to a lower frequency by integer division.The prescaler takes the basic timer clock frequency (which may be the CPU clock frequency or may be some higher or lower frequency) and divides it by some value before feeding it to the timer, according to how the prescaler register(s) are .The phase-locked loop (PLL) block is a feedback control system that automatically adjusts the phase of a locally generated signal to match the phase of an input signal. PLLs operate by producing an oscillator frequency to match the frequency of an input signal.

what is pll in microcontroller|What is a Phase

PH0 · What is a Phase

PH1 · What Is a Phase

PH2 · What Exactly Is a Phase

PH3 · Precision labs series: Phase lock loop fundamentals

PH4 · Phase Locked Loop (PLL)

PH5 · Phase Locked Loop

PH6 · Phase

PH7 · MT

PH8 · 6.9: Phase Locked Loop (PLL)